Manual P/N 454-44000

BVM Limited, Hobb Lane, Hedge End, Southampton, SO30 0GH, UK. TEL: +44 (0)1489 780144 FAX: +44 (0)1489 783589 E-MAIL: sales@bvmltd.co.uk WEB: http://www.bvmltd.co.uk

User's Manual

# BVME4000/6000

MC68040/68060 SINGLE BOARD COMPUTER

> Board Revision F Manual Revision I 21 February 2001

This material contains information of proprietary interest to BVM Ltd. It has been supplied in confidence and the recipient, by accepting this material, agrees that the subject matter will not be copied or reproduced, in whole or in part, nor its contents revealed in any manner or to any person except to meet the purposes for which it was delivered.

This page is intentionally left blank.

#### DISCLAIMER

The information in this document has been checked and is believed to be entirely reliable, however no responsibility is assumed for inaccuracies. BVM Ltd. reserves the right to make changes and/or improvements in both the product and the product documentation without notice. BVM Ltd. does not assume any liability arising out of the application or use of any product described herein; neither does it convey any licence under its patent rights or the rights of others.

#### USE OF PRODUCT

This product has been designed to operate in a VMEbus and IndustryPack<sup>™</sup> compatible electrical environment. Insertion of the board into any slot which is not VMEbus compatible is likely to cause serious damage. Insertion and removal of the board from the backplane or IndustryPack(s)<sup>™</sup> or cable(s) from the board must not be done whilst in a powered condition.

Do not lever out any devices from the product, which uses surface-mounted devices extensively, as these can be fractured by excessive force.

This product uses devices sensitive to static electricity. Ensure adequate static electricity precautions are observed when handling the product and associated devices.

#### RF. INTERFERENCE

This product complies with European Council Directive 89/336/EEC (EMC directive), and conforms to EN55022:1995 Class B (Limits and methods of measurement of radio interference characteristics of information technology equipment) and EN50082-1:1992 (Electromagnetic compatibility - Generic immunity standard, Part 1: residential, commercial and light industry) when used in accordance with the BVM EMC Guidelines Manual part number 454-77000 (available on request from BVM Ltd.).

#### GENERAL NOTICES

UNPACKING AND INSPECTION

This product contains components which are susceptible to static discharge, and should be handled with appropriate caution.

Upon receipt of this product, visually inspect the board for missing, broken or damaged components and for physical damage to the printed circuit board or connectors. This product was shipped in perfect physical condition. Any physical damage to the product is the responsibility of the shipping carrier and should be reported to the carrier's agent immediately.

#### RETURN OF GOODS

Before returning a product for repair, verify as well as possible that the suspected unit is at fault. Then call BVM Ltd. for a Customer Return (CR) number. Carefully package the unit, in the original shipping carton if this is available, and ship prepaid and insured, preferably by courier, with the CR number written on the outside of the package.

Include a return address and the telephone number of a technical contact, and a detailed description of the observed fault. For out-of-warranty repairs, a purchase order for repair charges must accompany the return. BVM Ltd. will not be responsible for damage due to improper packaging of returned items. Out of warranty repairs can be arranged, and will be charged on a material and labour basis, subject to a minimum repair charge. Return transportation and insurance will be charged as part of the repair and is in addition to the minimum charge.

#### SOFTWARE LICENCE NOTICE

Any software that is provided as Copyright BVM Ltd. is proprietary and confidential property of BVM Ltd., and each single copy is given on the agreed understanding that it is licensed for use on product combinations supplied by BVM Ltd. or their appointed distributors only. The software product may not be copied (except for backup purposes), given away, rented, loaned, reproduced, distributed or transmitted in any way or form, in whole or in part, without written permission of BVM Ltd. This applies to any merged, modified or derivative version of the software including but pot limited to versions

of the software including, but not limited to, versions produced by customising, translating, reverse engineering, decompiling or disassembly.

This licence may be automatically terminated without notice if any of its provisions are breached. Reasonable legal costs may be awarded to the prevailing party in connection with this licence agreement. Use of, or accepted delivery of these products shall constitute your acceptance of the provisions of this licence agreement.

#### WARRANTY

A) BVM Ltd. warrants that the articles furnished hereunder are free from defects in material and workmanship for one year after the date of shipment.

B) All warranties and conditions, express and implied, statutory and otherwise, as to the quality of the goods or their fitness for any purpose are hereby excluded and with the exception of liability for death or personal injury caused by negligence as defined in the Unfair Contract Terms Act 1977 the seller shall not be liable for any loss, injury or damage arising directly or indirectly from the use, application or storage of such goods.

C) Subclause (B) above shall not apply where the buyer deals as a consumer as this expression is defined in the Unfair Contract Terms Act 1977.

D) The liability of BVM Ltd. hereunder shall be limited to repair or replacement at the manufacturers discretion of any defective unit. Equipment or parts which have been subject to abuse, misuse, accident, alteration, neglect, unauthorised repair or installation are not covered by this warranty. BVM Ltd. shall have the right of determination as to the existence and cause of any defect.

E) The warranty period of the replacement or a repaired product or part shall terminate with the termination of the warranty period with respect to the original product or part for all replacement parts supplied or repairs made during the warranty period.

F) Although BVM Ltd. offer a high level of technical support and advice, due to the complex nature and wide application of product configurations it is the responsibility of the purchaser to be satisfied at the time of purchase that the products are suitable for the final application.

G) The term 'Software' used herein is defined as 'any program data or code in source or binary format recorded in or on any readable device or media'.

H) BVM Ltd. will effect all reasonable effort to resolve accepted reproducible software errors reported within 12 months of purchase. Acceptance of an error shall solely be based on conformance to supporting specifications. Proper operation of earlier releases is not guaranteed.

#### NOTICES

Copyright © 1993,1995,1998,2001 by BVM Ltd.

OS-9 is a registered trademark of Microware Systems Corporation.

VxWorks is a registered trademark of Wind River Systems Inc.

IndustryPack is a registered trademark of Greenspring Computers.

# WARNINGS

**Do not lever out the EPROM's from the BVME4000/6000.** The board uses surface-mounted devices extensively, which can be fractured by excessive force. Use proper EPROM extraction and insertion tools. **Damage may result if users attempt to remove or fit EPROM's incorrectly.**

**Do not lever out the IP's from the BVME4000/6000.** The board uses surface-mounted devices extensively, which can be fractured by excessive force. **Damage may result if users attempt to remove or fit IP's incorrectly.**

**Do not lever out memory modules from the BVME4000/6000.** The board uses surface-mounted devices extensively, which can be fractured by excessive force. Memory modules are not a field-fit option. **Damage may result if users attempt to remove or fit memory modules incorrectly.**

Do not fit/remove the 68040/68060 device to/from the BVME4000/6000. Special tools are required to fit and remove these devices and the correct voltage settings must be selected. Return the board to the factory if the 68040/68060 device requires changing. Damage may result if users attempt to fit or remove the 68040/68060 device.

**The BVME4000/6000 uses devices sensitive to static electricity.** Ensure adequate static electricity precautions are observed when handling the BVME4000/6000, EPROM's, IP's and memory modules.

Ensure the correct polarity of connections to the BVME4000/6000. In particular ensure the correct polarity of connections to the P2 I/O connector, incorporating the SCSI connections. Damage may result if users fail to observe correct connection polarity to the BVME4000/6000.

| Table | Of | Contents |  |

|-------|----|----------|--|

|       |    |          |  |

|       |    |          |  |

| l able Of | Contents |

|-----------|----------|

|           |          |

|           |          |

|           |          |

|           |          |

|           |          |

|           |          |

| <u>Co</u> | ntents F                                        | <u>age</u> |

|-----------|-------------------------------------------------|------------|

| 1.        | Introduction                                    | 1          |

|           | 1.1 Scope                                       | 1          |

|           | 1.2 BVME4000 Part Numbers                       | 1          |

|           | 1.3 BVME6000 Part Numbers                       | 1          |

|           | 1.4 Memory Module Part Numbers                  | 1          |

| 2         | Overview                                        | 2          |

|           | 2.1 Board Layout                                |            |

|           | 2.2 Features                                    |            |

|           | 2.3 Applications                                |            |

| 3.        | Description                                     |            |

| 5.        | 3.1 Block Diagram                               |            |

|           | 3.2 Processor                                   |            |

|           | 3.3 Memory                                      |            |

|           | 3.4 Real Time Clock                             |            |

|           | 3.5 Serial Communications                       | -          |

|           | 3.6 Parallel Port                               |            |

|           | 3.7 SCSI Interface                              |            |

|           | 3.8 Ethernet Interface                          |            |

|           | 3.9 IP I/O                                      |            |

|           | 3.10 VMEbus Interface                           |            |

|           | 3.10 VMEbus Metrace                             |            |

|           | 3.10.2 VMEbus Slave                             |            |

|           |                                                 |            |

|           | 3.11 Interrupts                                 |            |

|           | 3.11.1 VMEbus Interrupt Handler                 |            |

|           |                                                 |            |

|           | 3.11.3 VMEbus Interrupter                       |            |

|           | 3.12 VMEbus System Controller Functions         |            |

|           | 3.13 Power Supply Monitor/Watchdog              |            |

|           | 3.14 Local Bus Monitor                          |            |

|           | 3.15 Configuration Switch                       |            |

|           | 3.16 EEPROM                                     |            |

| 4.        | Installation                                    |            |

| 5.        | Configuration                                   |            |

|           | 5.1 PCB Layout                                  | .11        |

|           | 5.2 Link and Switch Definitions                 |            |

|           | 5.2.1 LK1 Abort Switch Enable                   | . 12       |

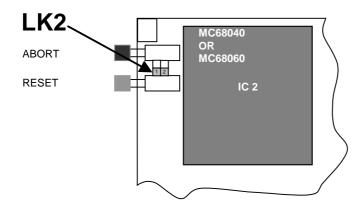

|           | 5.2.2 LK2 Reset Switch Enable                   | . 12       |

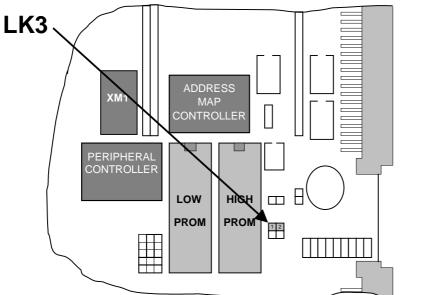

|           | 5.2.3 LK3 VMEbus Reset Out Enable               | . 13       |

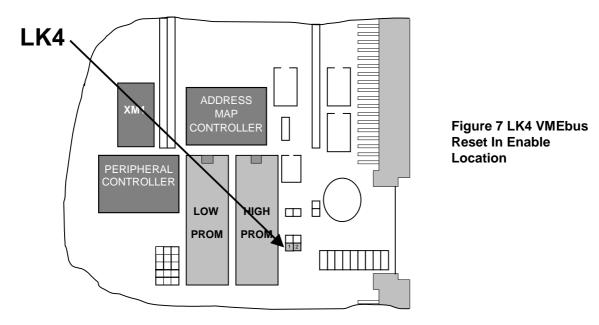

|           | 5.2.4 LK4 VMEbus Reset In Enable                | . 13       |

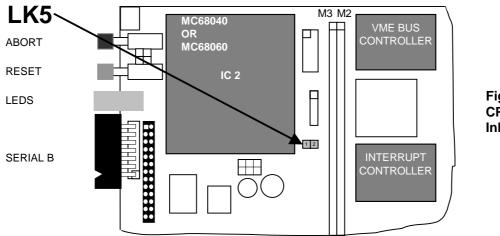

|           | 5.2.5 LK5 CPU Cache Inhibit                     | . 14       |

|           | 5.2.6 LK6 Cheapernet Heart Beat Enable          | . 14       |

|           | 5.2.7 LK7,8,9 Ethernet AUI/Cheapernet Select    | . 15       |

|           | 5.2.8 LK10,11,12,14,15 EPROM Size & Type Select | . 15       |

|           | 5.2.9 LK13 SCSI Termination Disable             | . 16       |

|           | 5.2.10 LK18,19 CPU 5/3.3V Selection             | . 16       |

|    | 5.2.11 LK21 SRAM Backup Selection           | . 17 |

|----|---------------------------------------------|------|

|    | 5.2.12 LK22 VMEbus System Controller Enable |      |

|    | 5.2.13 Configuration Switch                 | . 18 |

|    | 5.3 Indicators                              | 18   |

|    | 5.3.1 Green LED - RUNNING                   | 18   |

|    | 5.3.2 Red LED - VMEbus Master Access        | . 18 |

| 6. | Connector Pinouts                           | 19   |

|    | 6.1 JP1 & JP2 Serial Port Connections       | 19   |

|    | 6.2 JP3 Parallel Port Connections           | 19   |

|    | 6.3 JP4 Cheapernet Connector                | 20   |

|    | 6.4 JP4 Optional 10BaseT Connector          | 20   |

|    | 6.5 JP5A/B IP A/B Connections               |      |

|    | 6.6 JP7 CPU Fan Power                       | 22   |

|    | 6.7 JP8 JTAG Connector                      | 22   |

|    | 6.8 J1 SCSI Connections                     | 22   |

|    | 6.9 J14 SCSI Peripheral Power Connections   | 23   |

|    | 6.10 P2 I/O Connections                     |      |

|    | 6.11 Protection Fuses                       | 24   |

| 7. | Programming                                 |      |

|    | 7.1 Address Map                             |      |

|    | 7.1.1 I/O Address Map                       |      |

|    | 7.2 Memory Module                           |      |

|    | 7.3 VMEbus Master Access                    |      |

|    | 7.3.1 A16:D16 (D08EO)                       |      |

|    | 7.3.2 A16:D32                               |      |

|    | 7.3.3 A24:D16 (D08EO)                       |      |

|    | 7.3.4 A24:D32                               |      |

|    | 7.3.5 A32:D16                               |      |

|    | 7.3.6 A32:D32                               |      |

|    | 7.4 SRAM                                    |      |

|    | 7.5 EPROM                                   |      |

|    | 7.6 SCSI Controller                         |      |

|    | 7.6.1 Overview                              |      |

|    | 7.6.2 Programming                           |      |

|    | 7.6.3 Hardware Specific Considerations      |      |

|    | 7.6.4 SCSI Controller Registers             |      |

|    | 7.6.5 SCSI Electrical Interface             |      |

|    | 7.7 Ethernet Controller                     |      |

|    | 7.7.1 Overview                              |      |

|    | 7.7.2 Programming                           |      |

|    | 7.7.3 PORT Access                           |      |

|    | 7.7.4 Channel Attention Access              |      |

|    | 7.7.5 Bus Error Handling                    |      |

|    | 7.7.6 SYSBUS Byte Requirements              |      |

|    | 7.7.7 Electrical Interface                  |      |

|    | 7.8 Interrupt Controller                    |      |

|    | 7.8.1 Overview                              |      |

|    | 7.8.2 Processor Interrupter                 |      |

|    | 7.8.3 VMEbus interrupter                    |      |

|    |                                             |      |

| 7.8.4 Interru     | ot Controller Registers                   | 36 |

|-------------------|-------------------------------------------|----|

| 7.8.4.1           | VMEIRQ Enable Register                    | 36 |

| 7.8.4.2           | VMEIRQ Vector Register                    | 36 |

| 7.8.4.3           | VMEIRQ Level Register                     | 37 |

| 7.8.4.4           | LOCIRQ Enable Register                    | 37 |

| 7.8.4.5           | ETHIRQ Enable Register                    | 37 |

| 7.8.4.6           | Local IRQ Status Register                 | 38 |

| 7.9 IP Controller | ·                                         | 39 |

| 7.9.1 Overvi      | 9W                                        | 39 |

| 7.9.2 IP Exp      | ansion Interface                          | 39 |

| 7.9.3 IP Inter    | rupts                                     | 39 |

|                   | y Space Address Map                       |    |

|                   | D Space Address Map                       |    |

|                   | troller Registers                         |    |

|                   | IRQ Level A0 Register                     |    |

| 7.9.6.2           | -                                         |    |

|                   | IRQ Level B0 Register                     |    |

|                   | IRQ Level B1 Register                     |    |

|                   | IP Clock Speed Select Register            |    |

|                   | IP SYNC Clock Select Register             |    |

|                   | ave Access Controller                     |    |

|                   | view                                      |    |

|                   | dard (A24) & Extended (A32) Accesses      |    |

|                   | LI/O (A16) Accesses                       |    |

|                   | rolling The Window Size                   |    |

|                   | Address Generation                        |    |

|                   | ess Control Registers                     |    |

|                   | -                                         |    |

|                   | A32VBA - A32 VMEbus Base Address Register |    |

|                   | A32MSK - A32 VMEbus Address Mask Register |    |

|                   | A24VBA - A24 VMEbus Base Address Register |    |

|                   | A24MSK - A24 VMEbus Address Mask Register |    |

|                   | A16VBA - A16 VMEbus Base Address Register |    |

|                   | A32LBA - A32 Local Base Address Register  |    |

|                   | A24LBA - A24 Local Base Address Register  |    |

|                   | ADDRCTL - Address Control Register        |    |

| -                 | on Switch                                 |    |

|                   | guration Switch Layout                    |    |

|                   | guration Switch Register                  |    |

|                   | Clock/Timers                              |    |

|                   |                                           |    |

|                   | ware Specific Considerations              |    |

| -                 | ramming                                   |    |

|                   | rt/Timer                                  |    |

|                   | view                                      |    |

|                   | A Usage                                   |    |

|                   | B Usage                                   |    |

|                   |                                           |    |

|                   | Ishake Pin Usage                          |    |

|                   | 3230 PI/T Registers                       |    |

| 7.14 Serial Com   | munications Controller                    | 56 |

| 7.14.1 Overview                                 | 56 |

|-------------------------------------------------|----|

| 7.14.2 Serial Clock Sources                     | 56 |

| 7.14.3 Programming                              | 57 |

| 8. Specifications                               | 58 |

| 8.1 On-Board Functions                          | 58 |

| 8.2 VMEbus Master                               | 58 |

| 8.3 VMEbus Slave                                | 58 |

| 8.4 VMEbus System Controller Functions          | 58 |

| 8.5 VMEbus Interrupts                           | 59 |

| 8.6 IP Functions                                | 59 |

| 8.7 Board Configuration                         | 59 |

| 8.8 Operating Environment                       | 59 |

| Appendix A Data Sheet & Manual References       | 60 |

| A.1 MC68040/68LC040/68EC040 User's Manual       | 60 |

| A.2 MC68060/68LC060/68EC060 User's Manual       | 60 |

| A.3 82596CA User's Manual                       |    |

| A.4 53C710 Data Manual & Programmers Guide      |    |

| A.5 DP8570A Data Sheet                          |    |

| A.6 Z85230 User's Manual                        |    |

| A.7 MC68230 Data Sheet                          |    |

| A.8 VMEbus Specification                        |    |

| A.9 RS422/485 Interface Module User's Manual    |    |

| A.10 AM29F040 Data Book                         |    |

| A.11 NMC24C02 Data Sheet                        |    |

| A.12 MEM390 Memory Module User's Manual         |    |

| A.13 MEM400 Memory Module User's Manual         |    |

| A.14 MEM480 Memory Module User's Guide          |    |

| A.15 MEM4SD Memory Module User's Guide          |    |

| A.16 EXP100 Quad IP Expansion User's Manual     |    |

| Appendix B CPU Cache Coherency and Bus Snooping |    |

| B.1 BVME4000 (MC68040)                          |    |

| B.2 BVME6000 (MC68060)                          | 64 |

| Appendix C Memory Module Pinout                 | 66 |

| Appendix D IP Expansion Interface Pinout        | 67 |

| Appendix E Thermal Management                   | 68 |

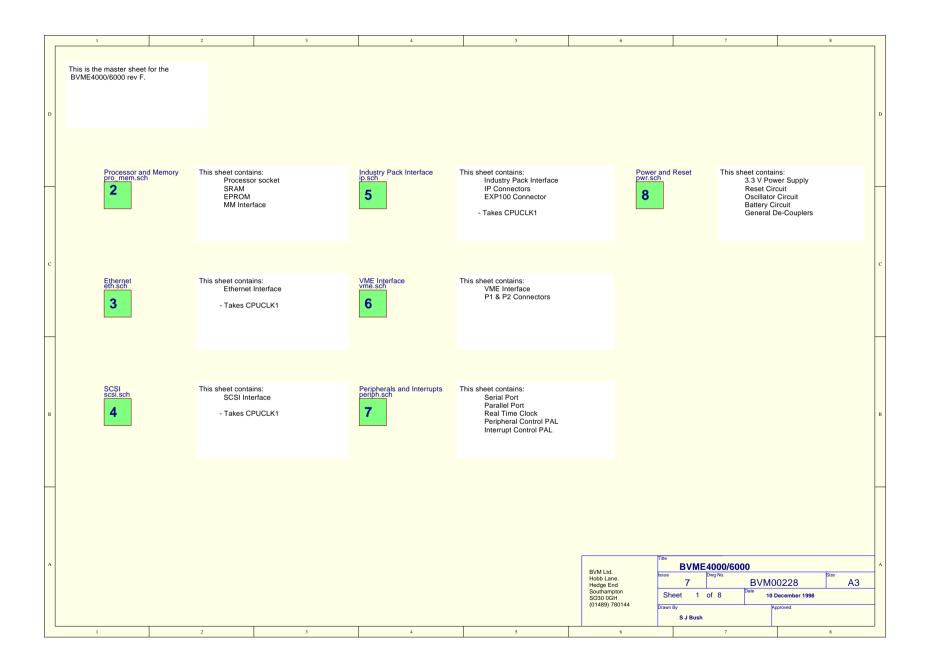

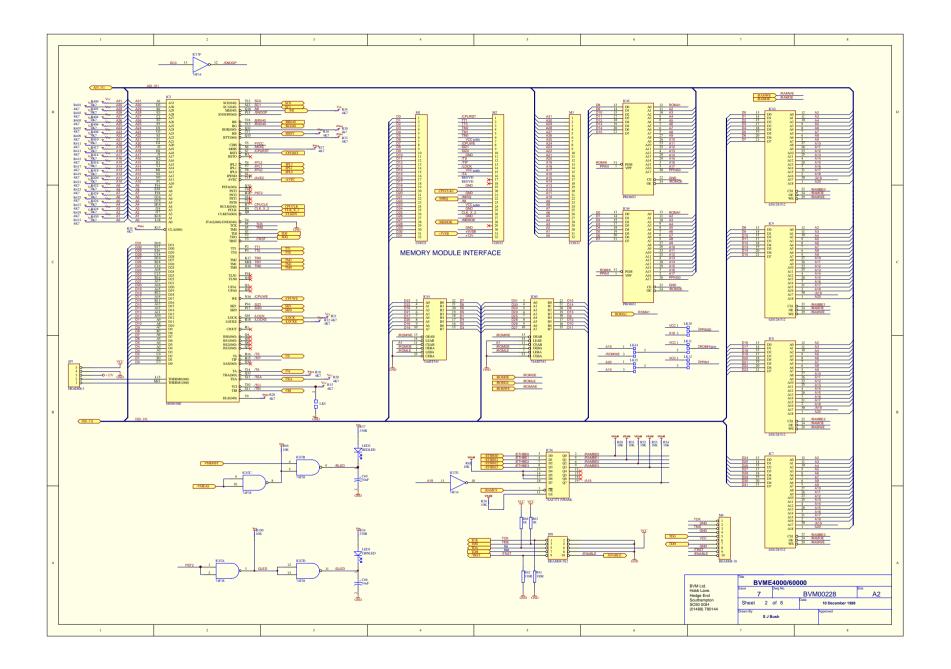

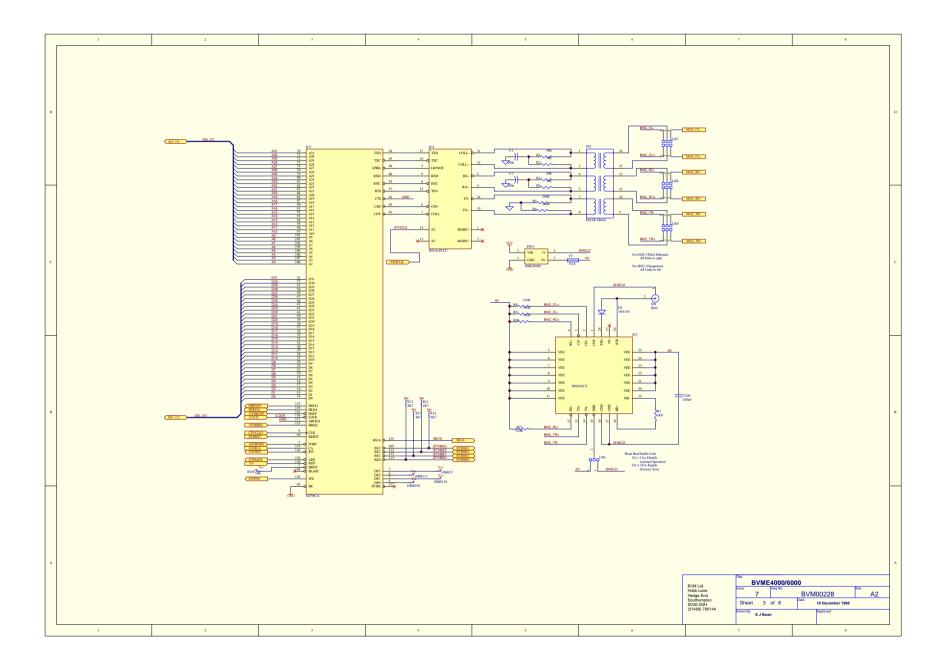

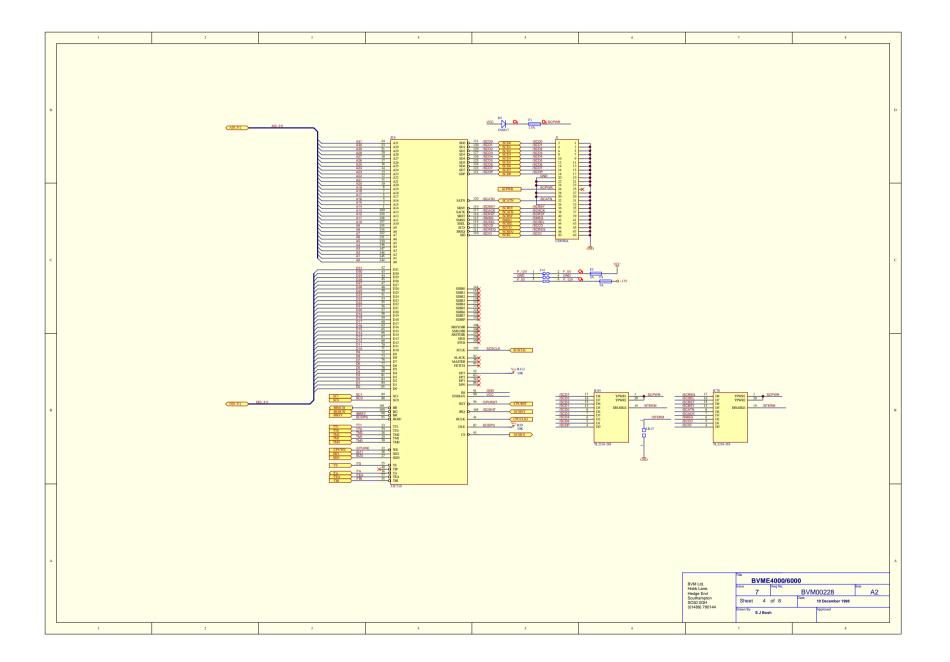

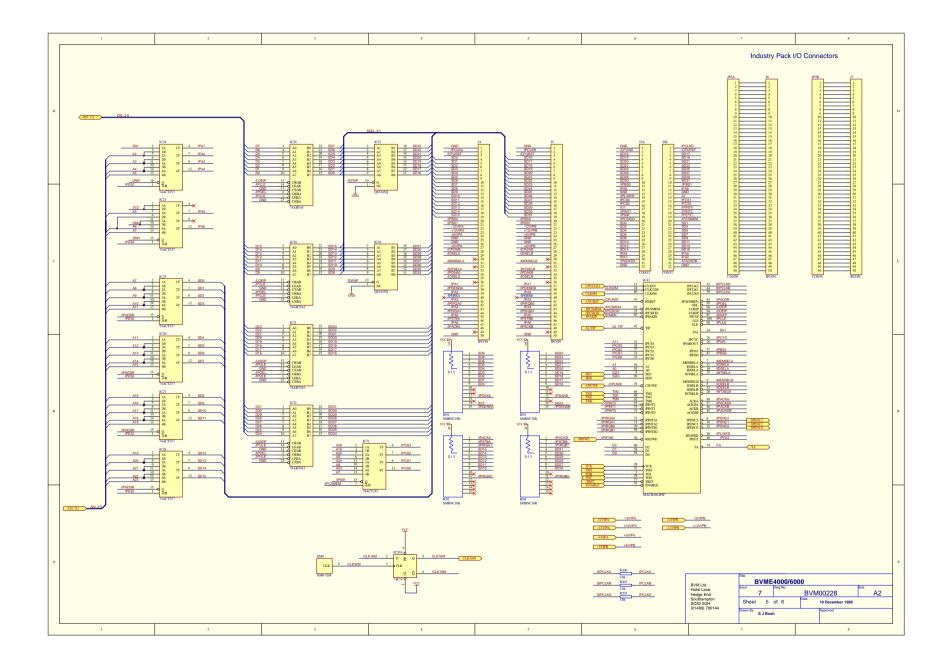

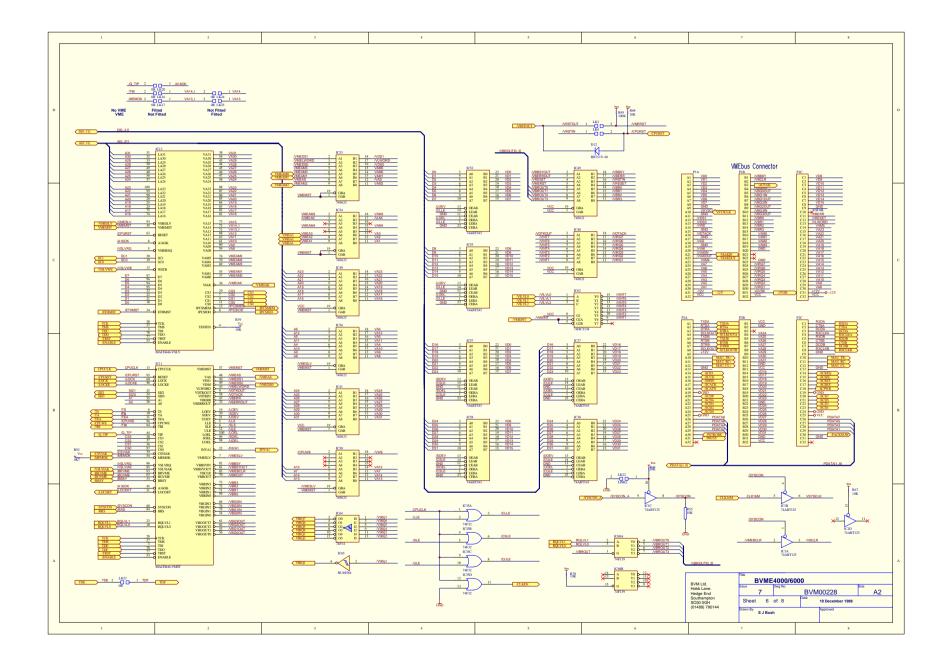

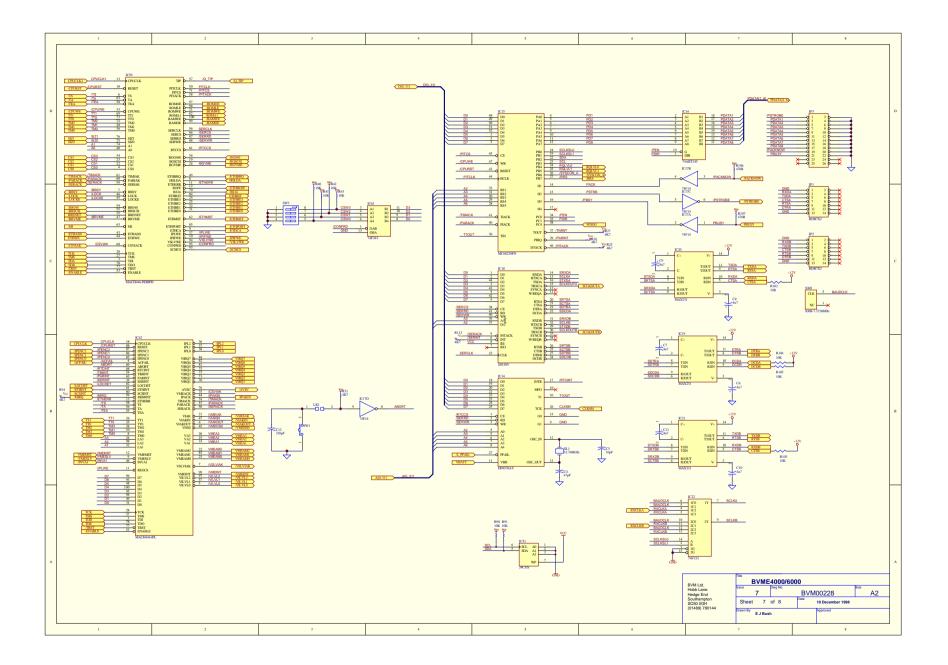

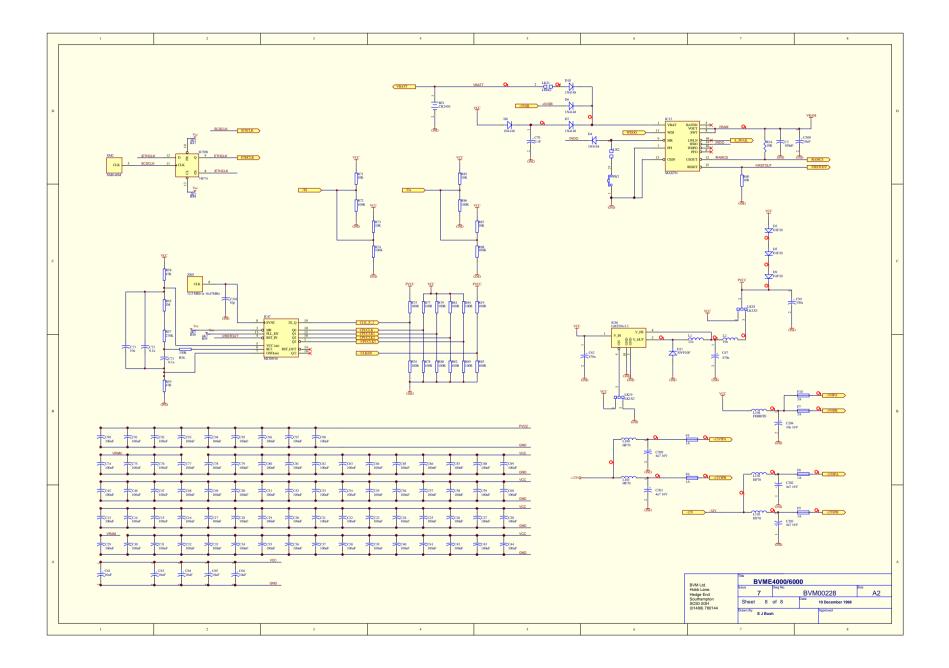

| Appendix F Circuit Diagrams                     | 69 |

# List of Figures

| Figure                                                                        | Page |

|-------------------------------------------------------------------------------|------|

| Figure 1 Board Layout                                                         | 2    |

| Figure 2 Block Diagram                                                        | 4    |

| Figure 3 PCB Layout                                                           | 11   |

| Figure 4 LK1 Abort Switch Enable Location                                     | 12   |

| Figure 5 LK2 Reset Switch Enable Location                                     | 12   |

| Figure 6 LK3 VMEbus Reset Out Enable Location                                 | 13   |

| Figure 7 LK4 VMEbus Reset In Enable Location                                  | 13   |

| Figure 8 LK5 CPU Cache Inhibit Location                                       | 14   |

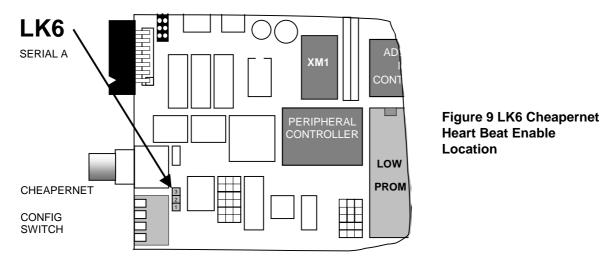

| Figure 9 LK6 Cheapernet Heart Beat Enable Location                            | 14   |

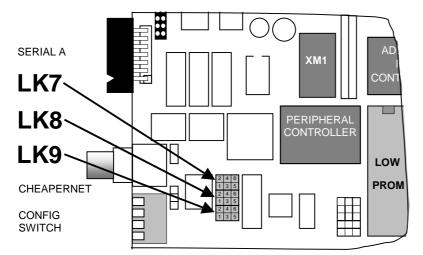

| Figure 10 LK7,8,9 Ethernet AUI/Cheapernet Select Location                     | 15   |

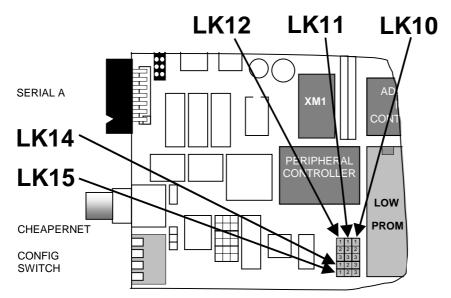

| Figure 11 LK10,11,12,14,15 EPROM Size & Type Select Location                  | 15   |

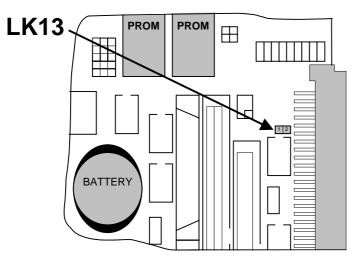

| Figure 12 LK13 SCSI Termination Disable Location                              | 16   |

| Figure 13 LK18,19 CPU 5/3.3V Selection Location                               | 16   |

| Figure 14 LK21 SRAM Backup Selection Location                                 | 17   |

| Figure 15 LK22 VMEbus System Controller Enable Location                       |      |

| Figure 16 Configuration Switch Location                                       | 18   |

| Figure 17 JP1 & JP2 Serial Port Connections                                   | 19   |

| Figure 18 JP3 Parallel Port Connections                                       | 19   |

| Figure 19 JP4 Optional 10BaseT Connector                                      | 20   |

| Figure 20 IP Connector Pin Numbering Viewed from solder side of BVME4000/6000 | 21   |

| Figure 21 Flat Cable Connector Pin Numbering Viewed from front of JP5         | 21   |

| Figure 22 JP7 CPU Fan Power                                                   |      |

| Figure 23 JP8 JTAG Connector                                                  |      |

| Figure 24 J1 SCSI Connections                                                 | 22   |

| Figure 25 J14 SCSI Peripheral Power Connections                               |      |

| Figure 26 Protection Fuse Positions                                           | 24   |

| Figure 27 Configuration Switch Layout                                         |      |

This page is intentionally left blank.

#### 1. Introduction

#### 1.1 Scope

This manual provides :-

A getting started guide. Configuration details. A user reference guide. A memory map. A map of all register locations. A detailed description of all dedicated registers. Details of implementation specific considerations for major devices. General hardware description.

This manual does not provide:-

Detailed data on the operation of the major devices. Details of VMEbus & IndustryPack<sup>™</sup> Specifications.

Information is provided to allow the module to be integrated into a system and configured by the system software. This User Manual is intended for use by system integrators, service personnel, software engineers and end users.

Unless otherwise stated, address information is in hexadecimal notation.

The term "IP" is used as an abbreviation for "IndustryPack™" throughout this manual.

#### 1.2 BVME4000 Part Numbers

452-40231/40331 MC68EC040 25/33MHz, VMEbus I/F, ETHERNET, SCSI, IP I/F, 2Mb SRAM 452-42231/42331 MC68040 25/33MHz, VMEbus I/F, ETHERNET, SCSI, IP I/F, 2Mb SRAM

Other versions of the BVME4000 are available to special order, where any of the VMEbus I/F, ETHERNET, SCSI & IP I/F may be omitted or 512Kb SRAM fitted. Contact your supplier for details.

#### 1.3 BVME6000 Part Numbers

452-40631

MC68EC060

66MHz, VMEbus I/F, ETHERNET, SCSI, IP I/F, 2Mb SRAM

452-42531

MC68060

50MHz, VMEbus I/F, ETHERNET, SCSI, IP I/F, 2Mb SRAM

Other versions of the BVME6000 are available to special order, where any of the VMEbus I/F, ETHERNET, SCSI & IP I/F may be omitted or 512Kb SRAM fitted. Contact your supplier for details.

#### 1.4 Memory Module Part Numbers

453-82390/83390 MEM390 25(50)/33(66)MHz 4Mbyte DRAM \*

| 453-82403/83403 | MEM400 25(50)/33(66)MHz | 16Mbyte DRAM & 4Mbyte FLASH |

|-----------------|-------------------------|-----------------------------|

| 453-82404/83404 | MEM400 25(50)/33(66)MHz | 16Mbyte DRAM & 8Mbyte FLASH |

|                 |                         |                             |

453-82482/83482 MEM480 25(50)/33(66)MHz 48Mbyte DRAM \*

453-85016/86016

MEM4SD 25(50)/33(66)MHz 16Mbyte SDRAM

453-87064/88064

MEM4SD 25(50)/33(66)MHz 64Mbyte SDRAM

453-87128/88128

MEM4SD 25(50)/33(66)MHz 128Mbyte SDRAM

453-89256/90256

MEM4SD 25(50)/33(66)MHz 128Mbyte SDRAM

Other Memory Module types and options are available, \* denotes type not recommended for new designs. Some Memory Module types can also be "stacked" two high, to increase capacity or mix memory types. Contact your supplier for details.

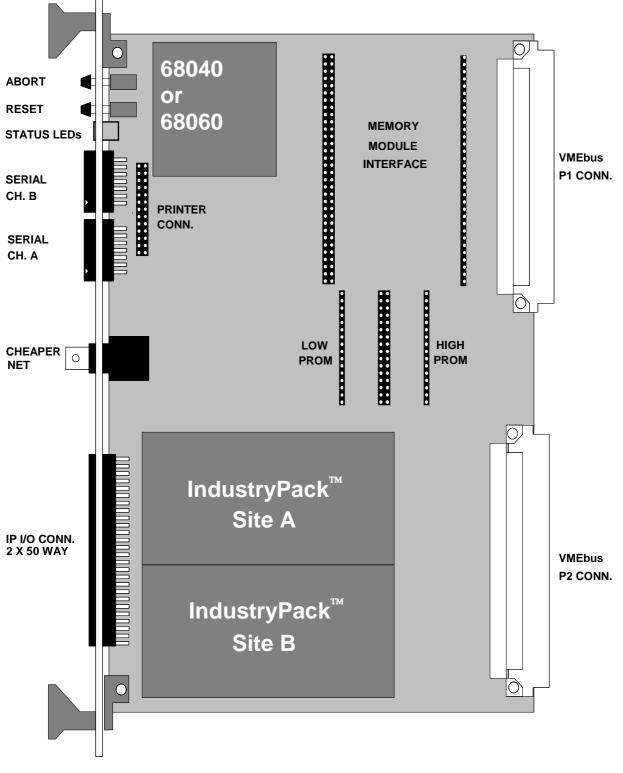

2.1 Board Layout

Figure 1 Board Layout

#### 2.2 Features

- BVME4000 MC68040 CPU (MC68EC040/68LC040 options).

Q 25 MHz and 33 MHz clock speed variants.

Q 4096 byte data and instruction caches.

- BVME6000 MC68060 CPU (MC68EC060/68LC060 options).

O 50 MHz and 66 MHz clock speed variants (25 MHz or 33 MHz bus).

O 8192 byte data and instruction caches.

- 32-bit wide burst fill Dual Ported (with Bus Snooping) memory module interface with NO capacity limitations allowing many options, for example:

38Mbytes of FLASH EPROM (Erasable, Programmable non-volatile storage).

256Mbytes DRAM.

- 2Mbyte EPROM pair (16-bit wide), supports 5V FLASH (1Mbyte).

- 512K/2Mbyte Non-volatile (battery backed) SRAM (32-bit wide).

- 2Kbit EEPROM (NMC24C02).

- High Performance DMA driven 5Mbyte/sec SCSI Interface (NCR53C710).

- High Performance DMA driven Ethernet/Cheapernet (10BaseT option) (82596CA).

- Two 16-bit IP Compatible Sites (Double height 32-bit access supported).

O Expansion Connector allowing 4 IP Compatible Site daughter board.

O 8MHz, 32MHz and proprietary high speed 'Source Synchronous Modes' supported.

- Two Interrupt driven serial I/O ports RS232, RS422 and RS485 options (Z85230).

- Real Time Clock (Battery backed) Including Tick timer, 2 16-bit timers and non-volatile configuration RAM (DP8570).

- Bi-directional Parallel port including one further 24-bit interrupting Counter/timer (MC68230).

- Optimised A32,A24,A16:D32,D16,D08 master/slave VMEbus interface.

VMEbus Interrupter.

VMEbus Interrupt handler.

Location monitor Mailbox Interrupts.

- VMEbus System Controller Functions.

O Four level Arbiter (programmable ROR, RWD and SGL).

O RESET, SYSCLK generator.

- Single slot, 6U form factor.

- Available built as a single solution disc based module.

- OS-9, VxWorks, Linux & debug monitor software support.

- Fully compatible to VMEbus specification revision C.1.

#### 2.3 Applications

- VMEbus Main System Processor.

- VMEbus Intelligent I/O Processor.

- High Performance Embedded Processor.

#### 3. Description

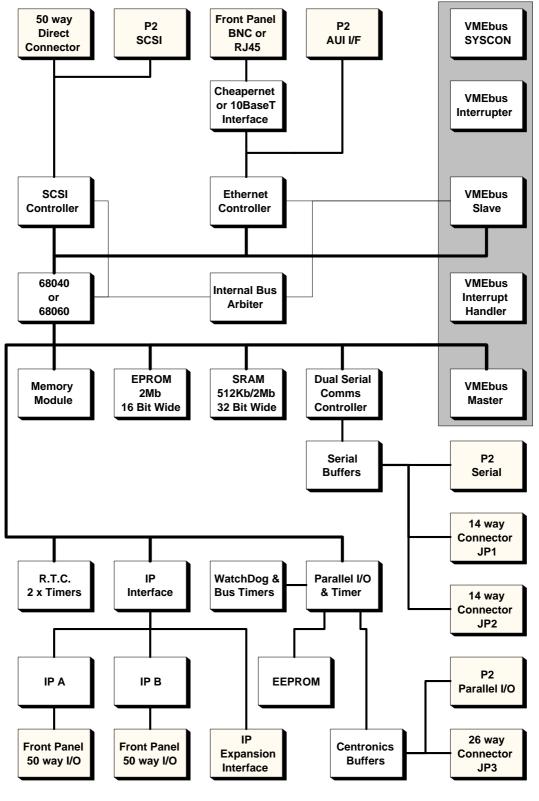

# 3.1 Block Diagram

Figure 2 Block Diagram

#### 3.2 Processor

The BVME4000 is based on the MC68040 32-bit processor from Motorola running at 25 or 33MHz. This virtual memory processor provides a MC68030 compatible integer processor running concurrently with an IEEE754 compatible floating-point unit (FPU). In addition two fully independent data and instruction demand page memory management units (MMU's) and two independent 4Kbyte caches provide efficient bus interface with a high degree of instruction execution parallelism.

The BVME6000 is similar to the BVME4000, but is based on the MC68060 32-bit processor from Motorola running at 50MHz with a 25MHz bus. The MC68060 provides a MC68040 compatible integer processor running concurrently with a MC68040 IEEE754 compatible floating-point unit (FPU). In addition two fully independent data and instruction MC68040 compatible demand page memory management units (MMU's) and two independent 8Kbyte caches.

The BVME4000 and BVME6000 are also available in lower cost versions with the MC68LC040/68LC060, which provide the same functionality as the MC68040/68060, but without the FPU, and with the MC68EC040/68EC060 which provide the same functionality, but without the MMU or FPU. The MC68LC060/68EC060 can run at 50 or 66MHz with a 25 or 33MHz bus respectively.

#### 3.3 Memory

The BVME4000/6000 may be fitted with a large variety of 32-bit wide, burst fill memory devices. The BVME4000/6000 uses the BVM memory module interface which provides a full 32-bit MC68040/68060 bus, and supports 2/1/1/1 (no wait state) accesses to a variety of standard BVM memory modules, allowing use of memory modules which currently include:

- 8 to 48Mbytes DRAM (5/3/3/3 access at 33MHz bus clock).

- 16 to 512Mbytes DRAM (4/1/1/1 read, 3/2/2/2 write at 25 & 33MHz bus clock).

- 16Mbytes DRAM plus 8Mbyte FLASH EPROM (4/2/2/2 DRAM, 5/2/2/2 FLASH access).

This memory can be dual ported allowing concurrent accesses by both the processor and other VMEbus masters. These accesses may be 'snooped' by the processor to maintain cache coherency. This, together with the onboard 'location monitor' allows full multiprocessor communication with other CPU (and DMA) VMEbus cards.

The BVME4000/6000 also provides 2Mbytes (512Kbytes to special order) of battery-backed 32-bit wide Static RAM, providing a 5 CPU clock cycle access at 25MHz or 33MHz bus clock. This SRAM may be used for non-volatile storage applications, or as main system memory in applications where a memory module is not fitted. The SRAM can also be dual ported to the VMEbus.

A pair of 32-pin JEDEC pinout sockets provide up to 2Mbytes of 16-bit wide EPROM providing a 10 CPU clock cycle access at 25MHz or 33MHz bus clock. These sockets can support 512K, 1M, 2M, 4M and 8Mbit EPROM devices, and up to 4Mbit 5V FLASH devices.

#### 3.4 Real Time Clock

The BVME4000/6000 provides a battery backed Real Time Clock using the DP8570 device. This device is battery backed, and maintains date and time data. The DP8570 can also generate an interrupt from it's periodic timer from 1mS to 1 second, or from two other independent 16-bit timers on chip. The timers offer a resolution of up to 500nS, and can be used in one-shot or periodic interrupt mode. A small amount of non-volatile storage is also provided for system configuration purposes. The DP8570 is battery backed using a lithium battery giving typically 10 years of non-volatile operation.

Two serial communications interfaces are provided from a Z85230 SCC device. The Z85230 provides both synchronous (SDLC/HDLC) and asynchronous protocols. Asynchronous baud rates of up to 115.2Kbit/s (using the on-board crystal) are supported. Field changeable buffer modules allow RS232, RS422 or RS485 electrical interfaces to be selected for either (or both) channels. The two serial interfaces are available on the front panel, or via the rear P2 connector. The synchronous clock signals are also available via the P2 connector.

## 3.6 Parallel Port

An 8-bit, bi-directional I/O port with interrupt driven handshake is provided allowing direct connection to Centronics devices. This is implemented in a 68230 which includes a further 24-bit timer with interrupt capability. This device also provides part of the board control functions, and is used to control the software watchdog function. The parallel port is connected to a dedicated connector near the front panel, or via the P2 connector.

## 3.7 SCSI Interface

A SCSI interface is provided built around the NCR53C710. This provides asynchronous transfers of up to 5Mbytes per second. The 32-bit DMA driven interface allows direct access to the entire memory map of the BVME4000/6000. The burst mode interface stacks up 16 bytes at a time and transfers them as a line transfer at up to 4/2/2/2 access speeds at 25MHz bus clock. At 5Mbyte/s this gives a 400nS burst every  $3.2\mu$ S or 12.5% bus bandwidth requirement. The 53C710 is an intelligent processor in its own right, running SCSI SCRIPTS software. This enables very high level commands to be issued to the SCSI interface further minimising processor overhead. The SCSI interface is connected to a dedicated 50-way connector and is also available via the P2 connector.

## 3.8 Ethernet Interface

An Ethernet Interface is provided built around the Intel 82596CA. This provides a 32-bit DMA driven interface to both Ethernet (via the AUI interface on the P2 connector) and either Cheapernet (via a front panel BNC) or optionally 10BaseT (via a front panel RJ45). The 32-bit DMA driven interface allows direct access to the entire memory map of the BVME4000/6000 allowing full packet management by the 82596CA. Each 32-bit transfer requires 320nS maximum (including arbitration) to execute the cycle. A transfer will occur no more frequently than every  $4\mu$ S (4 bytes at 1Mbyte per second). Thus worst case bus bandwidth requirement is 8% at 25MHz bus clock.

#### 3.9 IP I/O

Two standard IP compatible sites are provided. The IP interface complies fully with the IP specification. The two sites may be used individually for single IP's which are accessed as 16-bit wide, or as a pair for double IP's, which are accessed as 32-bit wide. IP operation is supported at 8MHz, 32MHz, and CPU synchronous speeds. The IP DMA function is not supported by these two sites, but may be supported on an IP daughter board (see below). The IP ID and I/O spaces are 256bytes each, and the memory spaces are 8Mbytes. IP vectored interrupts are fully supported and the interrupt levels may be individually programmed.

An IP expansion bus connector is provided to allow additional IP's to be supported. A further 4 IP's may be added on a daughter board connected to this expansion interface. Two 'virtual IP' sites are also available for controlling the daughter board IP interface. The daughter board may include a local DMA controller and RAM which is accessed through one of the 'virtual IP' sites, thus supporting the IP DMA function.

#### 3.10 VMEbus Interface

Full VMEbus system controller functions are provided including SYSCLK drive, Bus time out monitor, SYSRESET drive and an efficient 4 level bus arbiter working in prioritised (PRI), single level (SGL), or round robin (RRS) arbitration modes.

#### 3.10.1 VMEbus Master

Byte or Word Master accesses may be made to the Standard (A24) and Short I/O (A16) address spaces, Byte, Word and Longword Master accesses may be made to the Extended (A32) address space. BVME4000/6000 Longword accesses to the A24 or A16 address space may be converted to two Word cycles, or proceed as a Longword cycle dependant upon the BVME4000/6000 address space accessed. Read Modify Write (RMW) cycles are supported for all of these accesses.

VMEbus arbitration is normally configured to be Release On Request (ROR) method. This may be changed to Release When Done (RWD) with a PLD change. Both schemes use FAIR requesting, ensuring each master has an equal chance of obtaining the bus. Digital bus busy filtering and arbitration interleaving is used to ensure premium arbitration performance.

#### 3.10.2 VMEbus Slave

The memory module and on-board SRAM are dual ported onto the VMEbus. The VMEbus base address, size of window and local base address are programmable for the A24 and A32 address spaces. The BVME4000/6000 responds to Byte and Word and Longword Slave accesses to the A32, A24 and A16 address spaces.

The BVME4000/6000 can snoop VMEbus slave accesses if enabled to do so. Thus although the CPU uses extensive caching, full coherency is maintained by the CPU providing any data that is 'stale' in the accessed memory - refer to "Appendix B CPU Cache Coherency and Bus Snooping (on page 62)".

A VMEbus location monitor is also supported in the A16 address space. This is a fixed 256byte window size, and the VMEbus base address is programmable. A local interrupt can be enabled when the A16 VMEbus window is accessed.

The BVME4000/6000 is compatible with VMEbus address pipelining and RMW cycles.

#### 3.11 Interrupts

#### 3.11.1 VMEbus Interrupt Handler

The BVME4000/6000 may be configured to respond to VMEbus interrupts on any of the 7 VMEbus interrupt levels. Each interrupt level may be programmed to be enabled or disabled individually.

A User vectored VMEbus interrupt causes the CPU to reply with a VMEbus Master interrupt acknowledge cycle. This cycle uses only the that is broadcast in a similar way to the addresses. The A1,2,3 address lines indicate the address level being handled.

The interrupting device returns an ID vector on the odd data byte. This is used as the user vector by the CPU.

#### 3.11.2 Internal Interrupts

Internal CPU interrupts are generated from a variety of sources, as detailed in the table below:

| Source               | Level        | Туре     |

|----------------------|--------------|----------|

| VMEIRQ7:1            | IRQ7:1       | Vectored |

| ACFAIL               | 7            | Auto     |

| ABORT                | 7            | Auto     |

| 8570 RTC             | 6            | Auto     |

| 68230 TIMER          | 5            | Vectored |

| MEMORY MODULE        | 4            | Auto     |

| 85230 SCC            | 3            | Vectored |

| 53C710 SCSI          | 3            | Auto     |

| 68230 PARALLEL       | 2            | Vectored |

| 82596CA ETHERNET     | 2            | Auto     |

| LOCATION MONITOR     | 1            | Auto     |

| IPA, IPB INT0 & INT1 | Programmable | Vectored |

| IP EXPANSION I/F     | Programmable | Vectored |

#### 3.11.3 VMEbus Interrupter

The BVME4000/6000 may generate VMEbus interrupts on any programmable single level 1-7 and responds with a software programmable ID to the subsequent interrupt acknowledge cycle. Writing the ID to the a vector register causes a VMEbus interrupt to be generated on the selected level. The BVME4000/6000 VMEbus interrupt ID vector may be programmed to suit the application.

## 3.12 VMEbus System Controller Functions

The BVME4000/6000 provides a number of system controller functions that may be enabled by programming the relevant registers, or by link selection.

#### RESET

Asserted if +5V falls below 4.65V and when a link is installed. VMEbus RESET has a minimum asserted period of 200mS.

#### ARBITRATION

The BVME4000/6000 can be programmed/link selected to provide SGL, PRI or RRS arbitration.

#### SYSCLK

The BVME4000/6000 can be programmed/link selected to provide a 16MHz VMEbus SYSCLK.

#### **BUS TIMER**

The BVME4000/6000 can be programmed/link selected to provide a 128µS Bus Timeout BERR signal.

#### 3.13 Power Supply Monitor/Watchdog

A MAX791 provides power up/power down control for the battery switching for the non-volatile RAM and processor RESET. It also provides a processor watchdog capability controlled via the Board Control Register. If enabled, the processor will be reset if the software fails to maintain pulses to the watchdog circuit.

#### 3.14 Local Bus Monitor

All bus cycles (including VMEbus arbitration requests) are timed by an on-board timer. If any cycle takes longer than 64 CPU clock cycles a Transfer Error Abort signal and bus error exception vector are generated. Thus the processor cannot simply hang-up as a result of invalid addresses being generated from software. The exception to this is for VMEbus accesses - these are timed by the VMEbus Timeout monitor.

#### 3.15 Configuration Switch

A 4-bit configuration switch is provided for software bootstrap detection. This switch does not affect the hardware directly, but is normally used by the software to set up the BVME4000/6000's configuration registers.

#### 3.16 EEPROM

An NM24C02 serial I<sup>2</sup>C EEPROM device provides 2Kbits of EEPROM storage for configuration settings. The NMC24C02 is accessed on the I<sup>2</sup>C serial bus via the Board Control Register.

#### 4. Installation

The BVME4000/6000 module is inserted into a vacant VMEbus slot. If it is to function as the system controller, then it should be positioned in slot 1. It passes through all VMEbus daisy chained arbitration signals.

IACK should be jumpered to IAKIN on the backplane at slot 1. All interrupt IAKIN to IAKOUT and BGIN to BGOUT signals should be jumpered across vacant slots to the right of the module.

If it is not the system controller, it may be located in any of the VMEbus slots to the right of the VMEbus system controller.

To install the BVME4000/6000:

- 1. Ensure all backplane jumpers associated with the slot for the BVME4000/6000 are removed.

- 2. Ensure the BVME4000/6000 module is correctly configured for the target system.

- 3. If the Parallel interface is to be used, plug in the parallel cable to JP3 (if not using the P2 connections).

- 4. Connect the SCSI cable to the 50 way SCSI connector on the BVME4000/6000 (if not using the P2 connections), ensure the correct polarity.

- 5. Insert the BVME4000/6000 module into the rack pushing the VMEbus connector fully home.

- 6. Secure the BVME4000/6000 into the rack with the two fixing screws top and bottom.

- 7. Plug in serial cables to JP1 and/or JP2 (if not using the P2 connections).

- 8. If using Cheapernet, connect the Cheapernet BNC-T connector to the BVME4000/6000 BNC connector or if using the optional 10BaseT, connect the RJ45 connector to the BVME4000/6000 RJ45 connector.

- 9. Connect the IP I/O connections to the two 50 way front panel connectors.

- 10. Ensure that the configuration switch is set up correctly for the software installation.

- 11. Ensure the correct application EPROM's are fitted.

Removal is the reverse of assembly.

If the test or application software fails, ensure that all installation instructions have been correctly carried out. Some typical reasons for incorrect operation are:-

- 1. Socketed components may become disturbed in transit. Push home all socketed components where suspect.

- 2. The BVME4000/6000 module uses the VMEbus Address modifier codes to determine address significance. Ensure the host CPU module produces the correct address modifier codes.

- 3. Ensure that all links are configured to the default set-up or that any alterations to the default are correctly configured.

- 4. Ensure that the VMEbus backplane (if used) is correctly configured with regard to the daisychain signal jumpers and the IACK termination jumpers (if any).

The BVME4000/6000 CPU requires adequate airflow across it to ensure correct operation. A heatsink may need to be fitted to the CPU - refer to "Appendix E Thermal Management (on page 68)" for more details.

## 5. Configuration

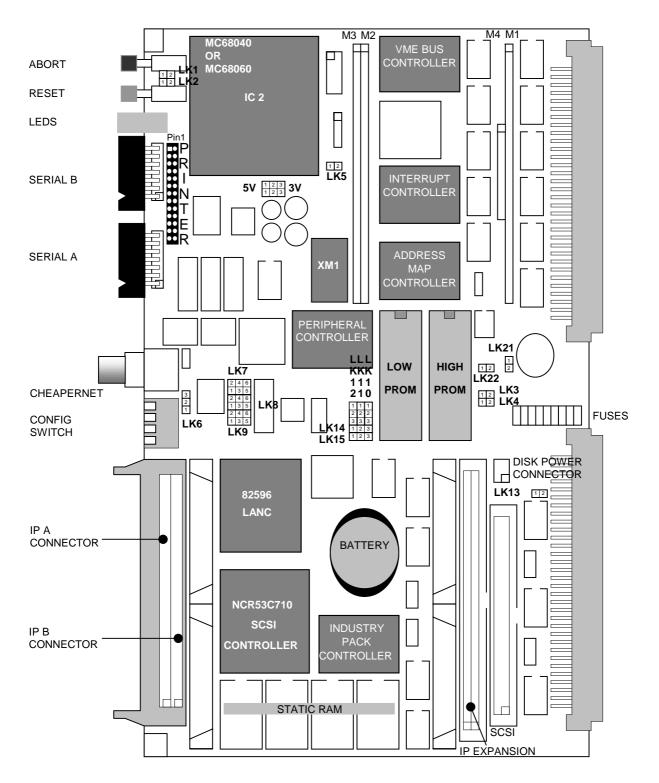

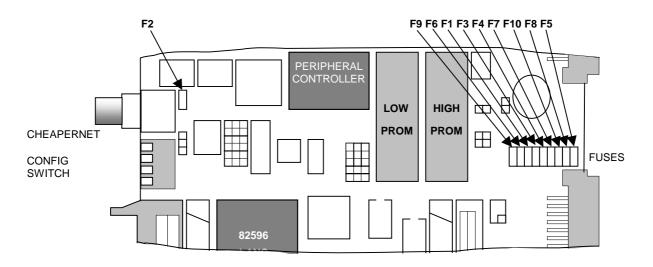

# 5.1 PCB Layout

Figure 3 PCB Layout

Copyright © 1993,1995,1998,2001 BVM Ltd.

# 5.2 Link and Switch Definitions

The following link definitions show the links grouped in the same orientation as the layout drawing on the previous page, i.e. with the VMEbus connectors to the right. Link positions marked with a S show the default configuration.

Some of the link numbers are not described here, these are for factory use only when configuring different build variants of the BVME4000/6000 and are not available for user's.

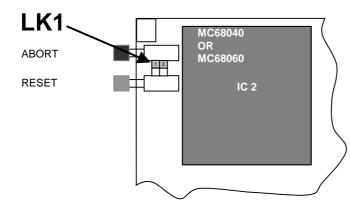

#### 5.2.1 LK1 Abort Switch Enable

Figure 4 LK1 Abort Switch Enable Location

Fitting this link enables the ABORT switch to generate interrupts.

| LK1            | Function                                         |

|----------------|--------------------------------------------------|

| 1 & 2 Fitted O | ABORT Switch generates Level 7 Auto-vectored IRQ |

| 1 & 2 Omitted  | NO IRQ generated from switch                     |

#### 5.2.2 LK2 Reset Switch Enable

Figure 5 LK2 Reset Switch Enable Location

Fitting this link enables the RESET switch to generate a local reset and (optionally) a VMEbus RESET.

| LK2            | Function                                       |

|----------------|------------------------------------------------|

| 1 & 2 Fitted O | RESET switch resets BVME4000/6000 (and VMEbus) |

| 1 & 2 Omitted  | NO RESET generated from switch                 |

#### 5.2.3 LK3 VMEbus Reset Out Enable

Figure 6 LK3 VMEbus Reset Out Enable Location

This link enables the VMEbus RESET to be driven by the BVME4000/6000 RESET signal.

| LK3            | Function                           |

|----------------|------------------------------------|

| 1 & 2 Fitted O | BVME4000/6000 RESET resets VMEbus  |

| 1 & 2 Omitted  | NO VMEbus RESET from BVME4000/6000 |

#### 5.2.4 LK4 VMEbus Reset In Enable

This link allows the BVME4000/6000 to be reset from the VMEbus RESET signal.

| LK4            | Function                                     |  |  |  |

|----------------|----------------------------------------------|--|--|--|

| 1 & 2 Fitted O | VMEbus RESET resets BVME4000/6000            |  |  |  |

| 1 & 2 Omitted  | NO BVME4000/6000 RESET generated from VMEbus |  |  |  |

#### 5.2.5 LK5 CPU Cache Inhibit

Figure 8 LK5 CPU Cache Inhibit Location

This link disables the MC68040/68060's on chip data and instruction caches to allow (for example) emulators to be used with the BVME4000/6000.

| LK5             | Function                      |

|-----------------|-------------------------------|

| 1 & 2 Fitted    | MC68040/68060 CACHES DISABLED |

| 1 & 2 Omitted O | MC68040/68060 CACHES ENABLED  |

#### 5.2.6 LK6 Cheapernet Heart Beat Enable

This link allows the CHEAPERNET Heartbeat function to be enabled.

| LK6   | Function                              |  |  |  |  |

|-------|---------------------------------------|--|--|--|--|

| 1&2 🖸 | Normal operation - Heartbeat Disabled |  |  |  |  |

| 2&3   | Heartbeat Enabled                     |  |  |  |  |

Note: this link is not fitted for the optional 10BaseT operation.

5.2.7 LK7,8,9 Ethernet AUI/Cheapernet Select

Figure 10 LK7,8,9 Ethernet AUI/Cheapernet Select Location

These links allow selection between CHEAPERNET (via front panel BNC connector) and ETHERNET AUI (via P2 connector). They must all be set in conjunction.

| LK7,8,9        | Function                       |

|----------------|--------------------------------|

| 1 & 3, 2 & 4 🗘 | CHEAPERNET via front panel BNC |

| 3 & 5, 4 & 6   | ETHERNET AUI via P2 connector  |

Note: these links are not fitted for the optional 10BaseT operation as it is permanently selected.

# 5.2.8 LK10,11,12,14,15 EPROM Size & Type Select

Figure 11 LK10,11,12,14,15 EPROM Size & Type Select Location

These links selects the size of EPROM in the IC44/45 32-pin EPROM sockets. A 27C512 (28-pin) EPROM should be fitted to the lower 28-pins of the socket (pins 1, 2, 31 & 32 unused).

| LK10 | LK11 | LK12 | LK14 | LK15 | Function                                   |

|------|------|------|------|------|--------------------------------------------|

| 1&2  | 1&2  | 1&2  | 1&2  | 1&2  | 27C512 (512Kbit) or 27C010 (1Mbit) devices |

| 2&3  | 1&2  | 1&2  | 1&2  | 1&2  | 27C020 (2Mbit) devices                     |

| 2&3  | 2&3  | 1&2  | 1&2  | 1&2  | 27C040 (4Mbit) devices                     |

| 2&3  | 2&3  | 2&3  | 1&2  | 1&2  | 27C080 (8Mbit) devices                     |

| 2&3  | 2&3  | 2&3  | 2&3  | 2&3  | AM29F010 / 020 / 040 Write Enable          |

| 2&3  | 1&2  | 2&3  | 2&3  | 2&3  | AM29F010 / 020 / 040 Write Protect         |

Figure 12 LK13 SCSI Termination Disable Location

This link allows the SCSI bus terminators to be enabled on the BVME4000/6000. This is necessary if the BVME4000/6000 is at the end of the SCSI bus cable, otherwise the terminators should be disabled.

| LK13            | Function                                 |  |  |  |

|-----------------|------------------------------------------|--|--|--|

| 1 & 2 Omitted O | SCSI bus terminated on BVME4000/6000     |  |  |  |

| 1 & 2 Fitted    | NO SCSI bus termination on BVME4000/6000 |  |  |  |

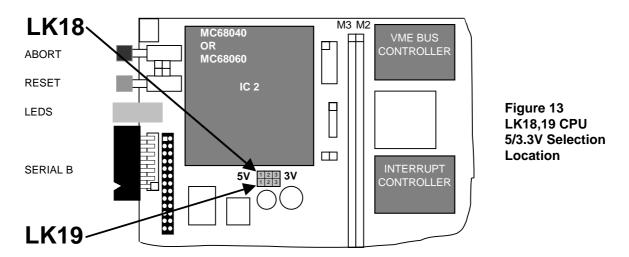

#### 5.2.10 LK18,19 CPU 5/3.3V Selection

These are factory set links – when a 68040 series CPU is fitted, 5V is selected, when a 68060 series CPU is fitted 3.3V is selected. They must all be set in conjunction.

Setting these links incorrectly will cause damage to the CPU device.

| LK18,19 (5V/3V) | Function                            |  |  |  |  |

|-----------------|-------------------------------------|--|--|--|--|

| 1&2             | 5 VOLTS SELECTED FOR 68040 SERIES   |  |  |  |  |

| 2&3             | 3.3 VOLTS SELECTED FOR 68060 SERIES |  |  |  |  |

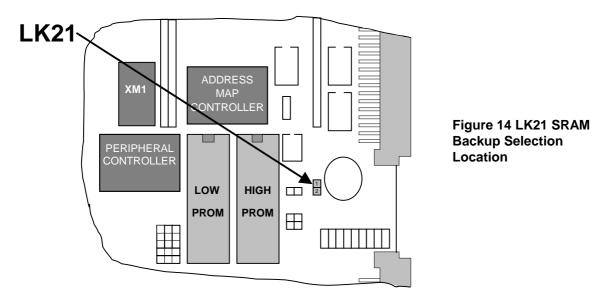

#### 5.2.11 LK21 SRAM Backup Selection

This link enables the SRAM to be backed up by the on-board battery. The SRAM is always backed up by the 0.1F Memory Capacitor and the VMEbus STDBY supply.

| LK21            | Function                                            |

|-----------------|-----------------------------------------------------|

| 1 & 2 Fitted    | SRAM is backed up by battery or MEMCAP/VMEbus STDBY |

| 1 & 2 Omitted O | SRAM is only backed up by MEMCAP/VMEbus STDBY       |

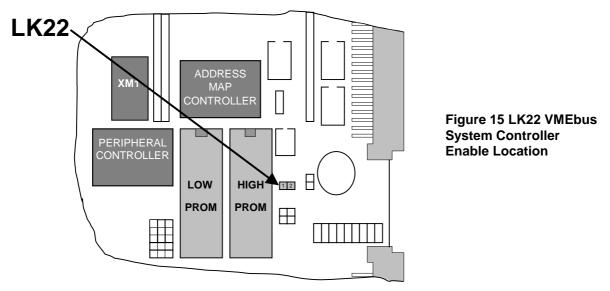

#### 5.2.12 LK22 VMEbus System Controller Enable

This link forces the BVME4000/6000 to be the VMEbus System Controller, so the BVME4000/6000 performs as the VMEbus arbiter, drives VMEbus SYSCLK and VMEbus BCLR. The normal selection for this function is in the Board Control Register when not overridden by this link - refer to "7.13.3 Port B Usage (on page 52)". Omitting this link is typically required to ensure that the VMEbus SYSCLK signal is driven as the VMEbus RESET signal is de-asserted.

| LK22           | Function                                          |

|----------------|---------------------------------------------------|

| 1 & 2 Omitted  | BVME4000/6000 VMEbus System Controller ENABLED    |

| 1 & 2 Fitted O | BVME4000/6000 VMEbus System Controller set in BCR |

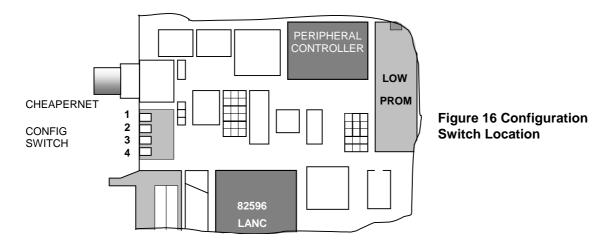

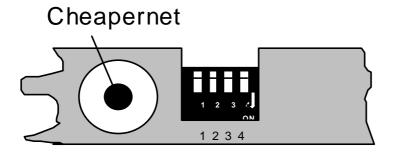

#### 5.2.13 Configuration Switch

This switch can be read by software to indicate system configuration options to the boot strap routines. A switch ON selects a logical 0 for a bit and a switch OFF selects a logical 1 for a bit. Switch pole 1 relates to Bit 3, switch pole 2 to Bit 2, switch pole 3 to Bit 1, and switch pole 4 to Bit 0 in the BVME4000/6000 Configuration Switch Register - refer to "7.11.2 Configuration Switch Register (on page 49)".

#### 5.3 Indicators

#### 5.3.1 Green LED - RUNNING

The GREEN RUNNING LED indicates that the BVME4000/6000 is running valid code. When extinguished, the processor is either halted or stopped. The LED will also dim when the processor is executing an RTE instruction, stacking an exception frame or doing an MMU table search.

#### 5.3.2 Red LED - VMEbus Master Access

The RED MASTER LED indicates that the BVME4000/6000 is currently an active VMEbus master.

#### 6. Connector Pinouts

## 6.1 JP1 & JP2 Serial Port Connections

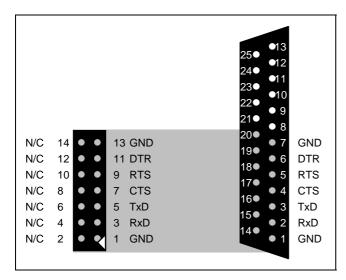

JP1 and JP2 carry the serial port signals for Serial Channel A and Serial Channel B respectively. JP1 (Serial Channel A) is the lower connector. The layout is designed to connect directly to a standard 25-way connector as shown:

The pinout numbering conventions are different for the two styles of connector (see diagram). However, the pinout is arranged to give a one to one connection to a 25-way D-type connector when using Insulation Displacement Connectors (IDC) and ribbon cable.

Not all the RS232 signals defined for a 25 way connector are supported by the BVME4000/6000. The cable assembly should be built such that pin 1 on the 14 way connector connects to pin 1 of the 25 way. A 14 way ribbon cable is used leaving pins 8 - 13 and 21 - 25 unconnected.

#### Figure 17 JP1 & JP2 Serial Port Connections

The above assumes standard RS232 drivers are fitted to the BVME4000/6000. If RS422 or RS485 interface modules are fitted refer to the RS422/RS485 INTERFACE MODULE documentation detailed in the "A.9 RS422/485 Interface Module (on page 60)" section of this manual .

## 6.2 JP3 Parallel Port Connections

JP3 carries the parallel port signals, and the layout is designed to connect directly to a standard 36-way connector as shown:

| /STROBE | 1  |   | • | 2  | GND | /STROBE | 1•  | ●19  |

|---------|----|---|---|----|-----|---------|-----|------|

| DATA1   | 3  | • | • | 4  | GND | DATA1   | 2●  | ●20  |

| DATA2   | 5  | ٠ | ٠ | 6  | GND | DATA2   | 3●  | •21  |

| DATA3   | 7  | • | • | 8  | GND | DATA3   | 4●  | •22  |

| DATA4   | 9  | • | ٠ | 10 | GND | DATA4   | 5●  | •23  |

| DATA5   | 11 | • | ٠ | 12 | GND | DATA5   | 6●  | •24  |

| DATA6   | 13 | ٠ | ٠ | 14 | GND | DATA6   | 7●  | ●25  |

| DATA7   | 15 | • | • | 16 | GND | DATA7   | 8●  | •26  |

| DATA8   | 17 | • | • | 18 | GND | DATA8   | 9●  | ●27  |

| /ACKNOW | 19 | ٠ | • | 20 | GND | /ACKNOW | 10● | •28  |

| BUSY    | 21 | • | ٠ | 22 | GND | BUSY    | 11● | •29  |

| N/C     | 23 | • | ٠ | 24 | N/C |         | 12● | • 30 |

| N/C     | 25 | • | • | 26 | N/C |         | 13● | •31  |

|         |    |   |   |    |     |         | 14• | • 32 |

|         |    |   |   |    |     |         | 15• | •33  |

|         |    |   |   |    |     |         | 16• | •34  |

|         |    |   |   |    |     |         | 17• | •35  |

|         |    |   |   |    |     |         | 18• | •36  |

|         |    |   |   |    |     |         |     |      |

|         |    |   |   |    |     |         |     | -    |

The pinout numbering conventions are different for the two styles of connector (see diagram). However, the pinout is arranged to give a one to one connection to a 36-way delta printer connector when using Insulation Displacement Connectors (IDC) and ribbon cable.

Not all the signals defined for a 36 way connector are supported by the BVME4000/6000. The cable assembly should be built such that pin 1 on the 26 way connector connects to pin 1 of the 36 way. A 26 way ribbon cable is used leaving pins 14 - 18 and 32 - 36 unconnected.

#### Figure 18 JP3 Parallel Port Connections

JP4 provides a  $50\Omega$  BNC connection to a 'Cheapernet' (IEEE802.3 10Base2) network.

When connecting to a network it is important that the bus topology is preserved. The Cheapernet bus is a multidrop bus with  $50\Omega$  terminators at each end. Ideally each station on the bus has a zero length stub connecting from the cable to the transceiver in the station. In practice, connection to the cable is made using a BNC T-piece connected to the BNC connector. The cable is broken at the point of contact and each new end is connected to the T-piece.

If the BVME4000/6000 is to be removed from the network, this is simply accomplished by disconnecting the BVME4000/6000 BNC connector (JP4) from the T-piece, leaving the T-piece connected to the cable.

All cheapernet cabling should use RG-58 type cable. It is important to ensure that both ends of the cable are terminated using  $50\Omega$  BNC terminators.

Note: JP4 may be replaced by an optional 10BaseT RJ45 connection.

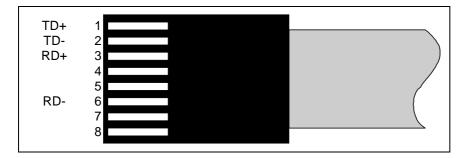

# 6.4 JP4 Optional 10BaseT Connector

The BVME4000/6000 may be fitted with an optional 10BaseT (twisted pair) Ethernet module. In this case the 10BaseT connection is permanently selected and the AUI is not available. The JP4 BNC connection is replaced with an RJ45 connector with the standard IEEE802.3 10BaseT pinout as shown:

Figure 19 JP4 Optional 10BaseT Connector

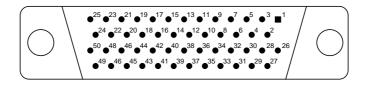

#### 6.5 JP5A/B IP A/B Connections

Each of the 50 pins on each I/O connector for the two IP, slots A and B, connects to a like-numbered pin on the two corresponding flat cable connectors, JP5A and JP5B on the BVME4000/6000 front panel. The IP I/O connector, the BVME4000/6000 flat cable connectors, and the wires on the ribbon cables are all numbered identically from 1 to 50.

Pin 1 on IP and BVME4000/6000 connectors are marked with a square pad, observable from the solder side of the respective board. Pin 1 is shown on JP5 by a triangle etched into the connector body. Pin 1 is typically marked on ribbon cable with a red stripe and on ribbon cable connectors with a manufacturer's mark, often a moulded textured triangle.

# Caution: This consistent pin numbering system is not maintained with many mass-terminated connectors. Each type of connector has its own intrinsic pin numbering system. Systems integrators or users making their own cables must be certain which pin corresponds to which signal.

The pin assignment of the IP I/O connector is fixed by the connector manufacturer and repeated in the IP Specification. This assignment is shown below.

# Figure 20 IP Connector Pin Numbering Viewed from solder side of BVME4000/6000

The pin assignment of the 50-way flat cable connectors JA and JB are shown below:

JP7 is a power connection for a CPU fan (if fitted). Normally this will not be required, but in environments where the air-flow is not sufficient, the airflow can be supplemented in this way. When a 68060 series CPU is being used, it's thermal output signals for variable-speed fans are also available on this connector. Refer to "Appendix E Thermal Management (on page 68)" for more details.

Figure 22 JP7 CPU Fan Power

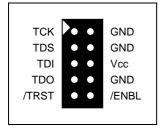

# 6.7 JP8 JTAG Connector

JP8 is a JTAG connection via a 2 x 5 way header, the pinout matching the MACH programming lead. This is for **factory use only**, to program the internal BVME4000/6000 logic devices.

Figure 23 JP8 JTAG Connector

#### 6.8 J1 SCSI Connections

|             |     | l      |

|-------------|-----|--------|

| /IO 50      | • • | 49 GND |

| /REQ 48     | • • | 47 GND |

| /CD 46      | • • | 45 GND |

| /SEL 44     | • • | 43 GND |

| /MSG 42     | • • | 41 GND |

| /RST 40     | • • | 39 GND |

| /ACK 38     | • • | 37 GND |

| /BSY 36     | ••  | 35 GND |

| GND 34      | • • | 33 GND |

| /ATN 32     | ••  | 31 GND |

| GND 30      | • • | 29 GND |

| GND 28      | • • | 27 GND |

| TERM PWR 26 | • • | 25 N/C |

| GND 24      | • • | 23 GND |

| GND 22      | • • | 21 GND |

| GND 20      | • • | 19 GND |

| /DP 18      | • • | 17 GND |

| /D7 16      | • • | 15 GND |

| /D6 14      | • • | 13 GND |

| /D5 12      | • • | 11 GND |

| /D4 10      | ••  | 9 GND  |

| /D3 8       | • • | 7 GND  |

| /D2 6       | • • | 5 GND  |

| /D1 4       | • • | 3 GND  |

| /D0 2       | ••  | 1 GND  |

|             |     | l      |

|             |     |        |

J1 carries the SCSI interface signals. The connector pinout allows a 50 way IDC and ribbon cable assembly to be directly connected. If necessary a standard 50-pin to 68-pin SCSI-1 to SCSI-3 adapter may be used to adapt to 68-pin SCSI devices.

Figure 24 J1 SCSI Connections

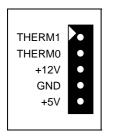

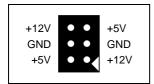

## 6.9 J14 SCSI Peripheral Power Connections

J14 provides a power pick up connection for SCSI devices integrated within a module with the BVME4000/6000. It can provide up to 2A of +5V and 2A of +12V. The pinout is arranged to be symmetrical allowing the mating connector to be plugged either way around.

#### Figure 25 J14 SCSI Peripheral Power Connections

#### 6.10 P2 I/O Connections

P2 is a 96 way, DIN-41612 connector consisting of 3 rows of 32 pins. The centre row (Row b) carries VMEbus 32-bit extension signals. The other two rows carry BVME4000/6000 specific I/O connections:

| P2 Connection | Row a             | Row c     |  |  |

|---------------|-------------------|-----------|--|--|

| 1             | TxDA              | RxDA      |  |  |

| 2             | RTSA              | CTSA      |  |  |

| 3             | DTRA              | DCDA      |  |  |

| 4             | SCLKOUTA          | SCLKINA   |  |  |

| 5             | TxDB              | RxDB      |  |  |

| 6             | RTSB              | CTSB      |  |  |

| 7             | DTRB              | DCDB      |  |  |

| 8             | SCLKOUTB          | SCLKINB   |  |  |

| 9             | +12V              | GND       |  |  |

| 10            | AUI-DO+           | AUI-DO-   |  |  |

| 11            | AUI-DI+           | AUI-DI-   |  |  |

| 12            | AUI-COLL+         | AUI-COLL- |  |  |

| 13            | GND               | GND       |  |  |

| 14            | SCSI-IO           | SCSI-REQ  |  |  |

| 15            | SCSI-CD           | SCSI-SEL  |  |  |

| 16            | SCSI-MSG          | SCSI-RES  |  |  |

| 17            | SCSI-ACK          | SCSI-BSY  |  |  |

| 18            | SCSI-ATN          | SCSI-TERM |  |  |

| 19            | GND               | GND       |  |  |

| 20            | SCSI-DP           | SCSI-D7   |  |  |

| 21            | SCSI-D6           | SCSI-D5   |  |  |

| 22            | SCSI-D4           | SCSI-D3   |  |  |

| 23            | SCSI-D2           | SCSI-D1   |  |  |

| 24            | SCSI-D0           | GND       |  |  |

| 25            | GND               | +5V       |  |  |

| 26            | PIO-7             | PIO-6     |  |  |

| 27            | PIO-5             | PIO-4     |  |  |

| 28            | PIO-3             | PIO-2     |  |  |

| 29            | PIO-1             | PIO-0     |  |  |

| 30            | /PIO-STRB PIO-ACK |           |  |  |

| 31            | PIO-BUSY GND      |           |  |  |

| 32            | N/C               | N/C       |  |  |

# 6.11 Protection Fuses

The connections on the BVME4000/6000 which provide output power are protected with fuses. These are surface-mounted fuses, and the BVME4000/6000 should be returned to factory for repair if any of these fuses blows. For reference, the following is a list of the fuses, their functions, positions, rating and type.

| Location    | Function      | Rating | Туре           |

|-------------|---------------|--------|----------------|

| (see below) |               |        | (LittleFuse)   |

| F1          | SCSI TERM PWR | 1.5A   | ALF II 42901.5 |

| F2          | ETHERNET -9V  | 200mA  | ALF II 429.200 |

| F3          | J14 +5V       | 2A     | ALF II 429002  |

| F4          | J14 +12V      | 2A     | ALF II 429002  |

| F5          | IP A +12V     | 1A     | ALF II 429001  |

| F6          | IP B +12V     | 1A     | ALF II 429001  |

| F7          | IP B +5V      | 2A     | ALF II 429002  |

| F8          | IP A -12V     | 1A     | ALF II 429001  |

| F9          | IP B -12V     | 1A     | ALF II 429001  |

| F10         | IP A +5V      | 2A     | ALF II 429002  |

**Figure 26 Protection Fuse Positions**

#### 7. Programming

#### 7.1 Address Map

The Address Map for the BVME4000/6000 is shown below. The BVME4000/6000 is byte addressed; each location addresses an 8-bit value. The BVME4000/6000 supports full 32-bit addressing for all four Local Bus Masters (the MC68040/68060 CPU, the 82596CA LANC, the 53C710 SCSI Controller and the VMEbus Slave Interface).

Some devices (IP memory, EPROM, SRAM, VMEbus A24) are dual mapped. This is to allow the Transparent Translation registers in the MC68040/68060 to provide alternative cache modes for accesses to these devices. The Cache Mode column is suggested cache mode, the hardware provides no implicit cache mode control.

| Address Range       | Device                     | Size                | Width   | Cache Mode        | Notes   |

|---------------------|----------------------------|---------------------|---------|-------------------|---------|

| 00000000 - variable | Memory Module or<br>SRAM   | variable            | D32     | copyback          | 1,2,4,6 |

| variable - CFFFFFFF | VMEbus - A32:D32           | up to 3328Mb        | D32     | write through     | 2       |

| D0000000 - DFFFFFFF | VMEbus - A32:D16           | 256Mb               | D16     | write through     |         |

| E0000000 - E7FFFFFF | IP Memory<br>(up to 8 IPs) | 128Mb               | D16:D32 | write through     | 5       |

| E8000000 - E8FFFFFF | EPROM                      | 16Mb<br>(2Mb valid) | D16     | write through     | 4,5     |

| E9000000 - E9FFFFFF | SRAM (alternate)           | 16Mb<br>(2Mb valid) | D32     | write through     | 3,5     |

| EA000000 - ECFFFFF  | Reserved                   | 48Mb                |         |                   |         |

| ED000000 - EDFFFFFF | VMEbus - A24:D32           | 16Mb                | D32     | write through     | 5       |

| EE000000 - EEFFFFF  | VMEbus - A24:D16           | 16Mb                | D16     | write through     | 5       |

| EF000000 - EFFFFFFF | Reserved                   | 16Mb                |         |                   |         |

| F0000000 - F7FFFFFF | IP Memory<br>(up to 8 IPs) | 128Mb               | D16:D32 | non-cached serial | 5       |

| F8000000 - F8FFFFFF | EPROM                      | 16Mb<br>(2Mb valid) | D16     | non-cached serial | 4,5     |

| F9000000 - F9FFFFFF | SRAM (alternate)           | 16Mb<br>(2Mb valid) | D32     | non-cached serial | 3,5     |

| FA000000 - FCFFFFFF | Reserved                   | 48Mb                |         |                   |         |

| FD000000 - FDFFFFFF | VMEbus - A24:D32           | 16Mb                | D32     | non-cached serial | 5       |

| FE000000 - FEFFFFFF | VMEbus - A24:D16           | 16Mb                | D16     | non-cached serial | 5       |

| FF000000 - FFFFFFFF | I/O see I/O map            | 16Mb                |         | non-cached serial |         |

#### NOTES:

- 1 If 'RAMLO' is set, then accesses to the bottom 512Kb/2Mb of this space access the Battery Backed SRAM.

- 2 The boundary between these spaces depends on how much memory is fitted to the memory module. Any space down here that is not decoded by the SRAM (if 'RAMLO' is set) or the memory module is decoded as a VMEbus A32:D32 access. This can be overridden if 'VMELO' is clear, in which case the bottom 256Mb are decoded as onboard (SRAM or memory module) accesses only.

- 3 If no memory module is fitted, this SRAM can be dual mapped, see note 1. The SRAM is always accessible at this location.

- 4 For the first two accesses after RESET the EPROM is dual mapped at 00000000.

- 5 These spaces are dual mapped in order to allow different caching modes to be set up using the MC68040/68060's Transparent Translation Registers.

- 6 The caching mode is programmable on 16Mb boundaries. Therefore if the amount of on board memory is not divisible by 16Mb, the bottom bit of the VMEbus A32:D32 space will have to be copy back cached. THIS MAY GIVE CACHE COHERENCY PROBLEMS as the processor is unable to snoop VMEbus space. In this case locate the VMEbus A32:D32 devices on a 16Mbyte boundary which will allow the transparent translation registers to be set up to give a coherent caching mode.

#### 7.1.1 I/O Address Map

| Address Range       | Device                     | Size | Width   |

|---------------------|----------------------------|------|---------|

| FF000000 - FF0FFFFF | SCSI Controller            | 1Mb  | D32     |

| FF100000 - FF1FFFFF | Ethernet Controller (LANC) | 1Mb  | D32     |

| FF200000 - FF2FFFFF | Interrupt Control          | 1Mb  | D8(OLW) |

| FF300000 - FF3FFFFF | IP Control                 | 1Mb  | D8(OLW) |

| FF400000 - FF4FFFFF | VME Slave Access Control   | 1Mb  | D8(OLW) |

| FF500000 - FF5FFFFF | Configuration Switch       | 1Mb  | D8(OLW) |

| FF600000 - FF7FFFFF | Reserved                   | 2Mb  |         |

| FF800000 - FF8FFFFF | IP I/O/ID space 1Mb        |      | D16:D32 |

|                     | (up to 8 IP's)             |      |         |

| FF900000 - FF9FFFFF | RTC                        | 1Mb  | D8(OLW) |

| FFA00000 - FFAFFFFF | Parallel Port              | 1Mb  | D8(OLW) |

| FFB00000 - FFBFFFFF | SCC                        | 1Mb  | D8(OLW) |

| FFC00000 - FFDFFFFF | Reserved 2Mb               |      |         |

| FFE00000 - FFEFFFFF | VMEbus A16 1Mb (64K wraps) |      | D32     |

| FFF00000 - FFFFFFFF | VMEbus A16 1Mb (64K wraps) |      | D16     |

#### 7.2 Memory Module

| Base Address | : | 0000000                  |

|--------------|---|--------------------------|

| Size         | : | Memory Module Dependent. |

The BVME4000/6000 provides a site for BVM Memory Modules - refer to "Appendix C Memory Module Pinout (on page 66)" for details. These modules are available in various configurations (DRAM, SRAM, FLASH) and sizes and access speeds. Refer to the relevant Memory Module documentation detailed in the "Appendix A Data Sheet & Manual References (on page 60)" section of this manual for details of the configuration.

The Memory Module Interface is 32-bits wide (though byte addressed) and supports Cache LINE transfers. Thus 'zero wait state' operation is supported; giving the MC68040/68060 optimum performance of 2/1/1/1 clock cycles per transfer. Thus 16 bytes of data can be transferred in 5 clock cycles (80Mbyte/sec @ 25MHz bus clock). Refer to the relevant Memory Module Manual for actual memory performance.

The Memory Module provides a 'memory present' (/MEMOK) signal during the first cycle of an access that it decodes. Thus the BVME4000/6000 address decoder automatically handles different size Memory Modules. Any accesses (for addresses up to CFFFFFF) that are not decoded by the Memory Module, generate a VMEbus A32:D32 master access (except if VMELO is clear, in which case the bottom 256Mb are decoded as on-board accesses only) - refer to "7.3.6 A32:D32 (on page 28)" for more details.

## 7.3 VMEbus Master Access

The BVME4000/6000 can access VMEbus as a bus master. Depending on the Address Range used, different types of access are performed.

VMEbus specifies three basic Address Mode schemes - A16 (Short I/O), A24 (Standard) and A32 (Extended). The BVME4000/6000 supports all of these modes.

VMEbus also specifies three basic Data Transfer schemes - D08(EO), D16 and D32. The BVME4000/6000 supports all these modes.

The BVME4000/6000 does not support Block transfers or A64:D64.

#### 7.3.1 A16:D16 (D08EO)

Base Address : FFFF0000. Size : 64Kbyte.

Accesses to this area perform a Short I/O access to VMEbus with LWORD inactive. Line and Long Word accesses are automatically broken down to Word (D16) cycles. Byte accesses produce a D08(EO) cycle. These accesses only involve signals available on the P1 VMEbus Connector.

The following Address Modifier (AM) codes are generated:

| CPU Supervisor | Data Access | = | \$2D |

|----------------|-------------|---|------|

| CPU User       | Data Access | = | \$29 |

#### 7.3.2 A16:D32

| Base Address | : | FFEF0000. |

|--------------|---|-----------|

| Size         | : | 64Kbyte.  |

Accesses to this area perform a Short I/O access to VMEbus with LWORD dependent on the access type. Line and Long Word accesses produce a D32 (LWORD active) cycle. Word accesses produce a D16 (LWORD inactive) cycle. Byte accesses produce a D08(EO) cycle. These accesses involve signals on both P1 and P2, therefore, a 'P2' Backplane is required.

The following Address Modifier (AM) codes are generated:

| CPU Supervisor | Data Access | = | \$2D |

|----------------|-------------|---|------|

| CPU User       | Data Access | = | \$29 |

#### 7.3.3 A24:D16 (D08EO)

Base Address : FE000000 or EE000000. Size : 16Mbyte.

Accesses to this area perform a Standard Address access to VMEbus with LWORD inactive. Line and Long Word accesses are automatically broken down to Word (D16) cycles. Byte accesses produce a D08(EO) cycle. These accesses only involve signals available on the P1 VMEbus Connector.

The following Address Modifier (AM) codes are generated:

| CPU Supervisor | Program Access | = | \$3E |

|----------------|----------------|---|------|

| -              | Data Access    | = | \$3D |

| CPU User       | Program Access | = | \$3A |

|                | Data Access    | = | \$39 |

### 7.3.4 A24:D32

| Base Address | : | FD000000 or ED000000. |

|--------------|---|-----------------------|

| Size         | : | 16Mbyte.              |

Accesses to this area perform a Standard Address access to VMEbus with LWORD dependent on the access type. Line and Long Word accesses produce a D32 (LWORD active) cycle. Word accesses produce a D16 (LWORD inactive) cycle. Byte accesses produce a D08(EO) cycle. These accesses involve signals on both P1 and P2, therefore, a 'P2' Backplane is required.

The following Address Modifier (AM) codes are generated:

| CPU Supervisor | Program Access | = | \$3E |

|----------------|----------------|---|------|

| -              | Data Access    | = | \$3D |

| CPU User       | Program Access | = | \$3A |

|                | Data Access    | = | \$39 |

#### 7.3.5 A32:D16

| Base Address | : | D0000000. |

|--------------|---|-----------|

| Size         | : | 16Mbyte.  |

Accesses to this area perform an Extended Address access to VMEbus with LWORD inactive. Line and Long Word accesses are automatically broken down to Word (D16) cycles. Byte accesses produce a D08(EO) cycle. These accesses involve signals on both P1 and P2, therefore, a 'P2' Backplane is required.

The following Address Modifier (AM) codes are generated:

| CPU Supervisor | Program Access | = | \$0E |

|----------------|----------------|---|------|

|                | Data Access    | = | \$0D |

| CPU User       | Program Access | = | \$0A |

|                | Data Access    | = | \$09 |

#### 7.3.6 A32:D32

Base Address

:

Immediately above the Memory Module, or 10000000 (if VMELO is clear).

Size

:

Maximum 3328Mbyte (Memory Module Dependent).

Accesses to this area perform a Standard Address access to VMEbus with LWORD dependent on the access type. Line and Long Word accesses produce a D32 (LWORD active) cycle. Word accesses produce a D16 (LWORD inactive) cycle. Byte accesses produce a D08(EO) cycle. These accesses involve signals on both P1 and P2, therefore, a 'P2' Backplane is required.

This address space can follow on contiguously from the top of a memory module, or the SRAM (if RAMLO is set), or can be set to start at a fixed base address (if VMELO is clear). This allows for a fixed partitioning of on-board and off-board memory for operating systems with this requirement. Refer to "7.10 VMEbus Slave Access Controller (on page 45)" for RAMLO and VMELO settings.

The following Address Modifier (AM) codes are generated:

| CPU Supervisor | Program Access | = | \$0E |